-

미리보기

1 / 7소개

"[01분반 1등의 보고서], [A+ 자료], [결보] 중앙대학교 전자회로설계실습 6. Common Emitter Amplifier 설계 결과보고서"에 대한 내용입니다.목차

1. 설계실습 내용 및 분석

2. 결론본문내용

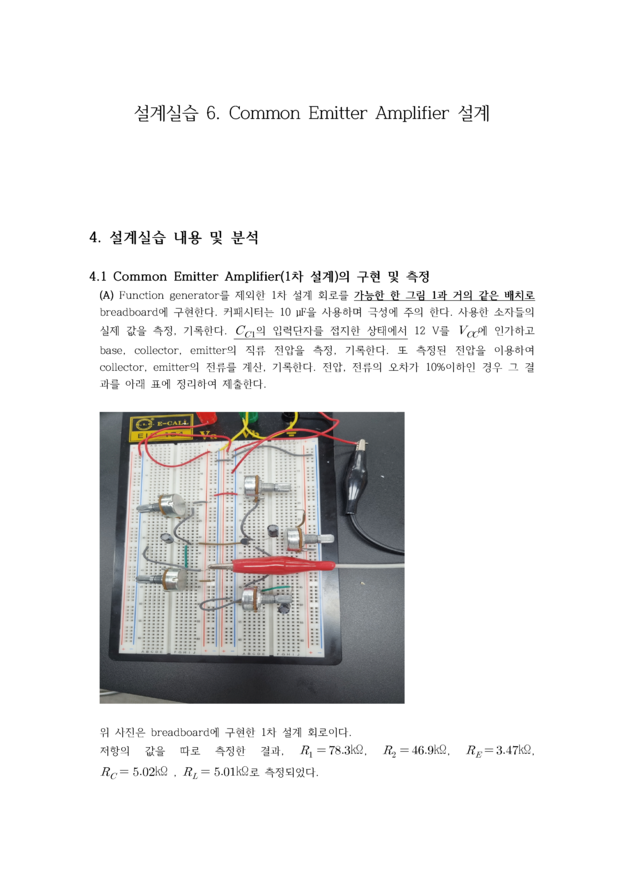

본 실험을 통해 Sedra/Smith 교재에 나오는 BJT Amplifier의 종류 중 하나인 Common Emitter Amplifier를 직접 설계해보았다(1차 설계). 또한 1차 설계에서는 이 에 관한 비선형함수 이므로 nonlinear distortion이 발생하는데 이러한 비선형 왜곡을 없애고 선형증폭기를 만드는 설계를 해보았다(2차 설계). 또한 를 10% 큰 값으로 변경했을 때와 10% 작은 값으로 변경했을 때의 과 의 값을 측정하여 gain을 구하고 수식으로 확인해 보았다.

본 설계실습에서 측정한 base, collector, emitter의 직류전압과 측정된 전압을 이용하여 계산한 base, collector, emitter의 전류는 4.1과 4.2에서 모두 10% 이내의 오차값을 보이며 비교적 정확한 값을 얻을 수 있었다.참고자료

· 없음태그

-

자료후기

-

자주묻는질문의 답변을 확인해 주세요

꼭 알아주세요

-

자료의 정보 및 내용의 진실성에 대하여 해피캠퍼스는 보증하지 않으며, 해당 정보 및 게시물 저작권과 기타 법적 책임은 자료 등록자에게 있습니다.

자료 및 게시물 내용의 불법적 이용, 무단 전재∙배포는 금지되어 있습니다.

저작권침해, 명예훼손 등 분쟁 요소 발견 시 고객센터의 저작권침해 신고센터를 이용해 주시기 바랍니다. -

해피캠퍼스는 구매자와 판매자 모두가 만족하는 서비스가 되도록 노력하고 있으며, 아래의 4가지 자료환불 조건을 꼭 확인해주시기 바랍니다.

파일오류 중복자료 저작권 없음 설명과 실제 내용 불일치 파일의 다운로드가 제대로 되지 않거나 파일형식에 맞는 프로그램으로 정상 작동하지 않는 경우 다른 자료와 70% 이상 내용이 일치하는 경우 (중복임을 확인할 수 있는 근거 필요함) 인터넷의 다른 사이트, 연구기관, 학교, 서적 등의 자료를 도용한 경우 자료의 설명과 실제 자료의 내용이 일치하지 않는 경우

함께 구매한 자료도 확인해 보세요!

-

전자회로설계 및 실습6_설계 실습6. Common Emitter Amplifier 설계_예비보고서 6페이지

1. 목적 Rsig Ω, RL kΩ, VCC V 인 경우, 인 NPN BJT를 사용하여 Ri n 이 kΩ단위이고 amplifier gain( )이 -100 V/V이며 emitter 저항 사용한 Common Emitter Amplifier를 설계, 구현, 측정, 평가한다. 2. 준비물 및 유의사항 Fun.. -

[A+예비보고서] 설계실습 7. Common Emitter Amplifier의 주파수 특성 8페이지

1. 목적 이전 실험에서 설계한 emitter 저항을 사용한 Common Emitter Amplifier의 주파수 특성 및 커패시터의 영향을 측정, 평가한다. 2. 준비물 및 유의사항 Function Generator 1대 DC Power Supply(2channel) 1대 Oscilloscope(2channel) 1대 DMM 1대 N.. -

[중앙대 전자회로설계실습]설계실습 6(Common Emitter Amplifier 설계) 결과보고서 5페이지

2. 설계실습 결과 (A) DC Bias 전압, 전류 측정 실습계획 시 설계한 Common Emitter Amplifier의 회로는 다음과 같다. 회로 구성 시 가변저항을 설계 값과 최대한 비슷하게 조정하여 구성하였다. 조정한 가변저항 측정값은 다음과 같다. -

설계실습 7. Common Emitter Amplifier의 주파수 특성 예비레포트 8페이지

3.2 주파수특성에 대한 R_E와 커패시터의 영향 (A) R_E를 +10%, -10%로 변경하고 20 mVpp 사인파를 입력하였을 때 10 Hz에서 Unit gain frequency까지의 주파수 응답특성을 제출하라. Overall gain의 최대값, 그리고 3 dB bandwidth와 unity gain frequency를 구하라. 어느 특성이 3.1(.. -

설계실습 6. Common Emitter Amplifier 예비레포트 8페이지

(A) 100KHz, 20mVpp 사인파를 이 증폭기에 인가하려면 function generator의 출력전압(Vpp)을 얼마로 설정해야 하는가? 앞의 “Oscilloscope와 Function Generator”에서 설명한 바와 같이 function generator의 화면에 표시되는 전압은 function generator의 출력단자에 부하 R_L=50..

문서 초안을 생성해주는 EasyAI